- State transition diagram altera quartus ii software#

- State transition diagram altera quartus ii code#

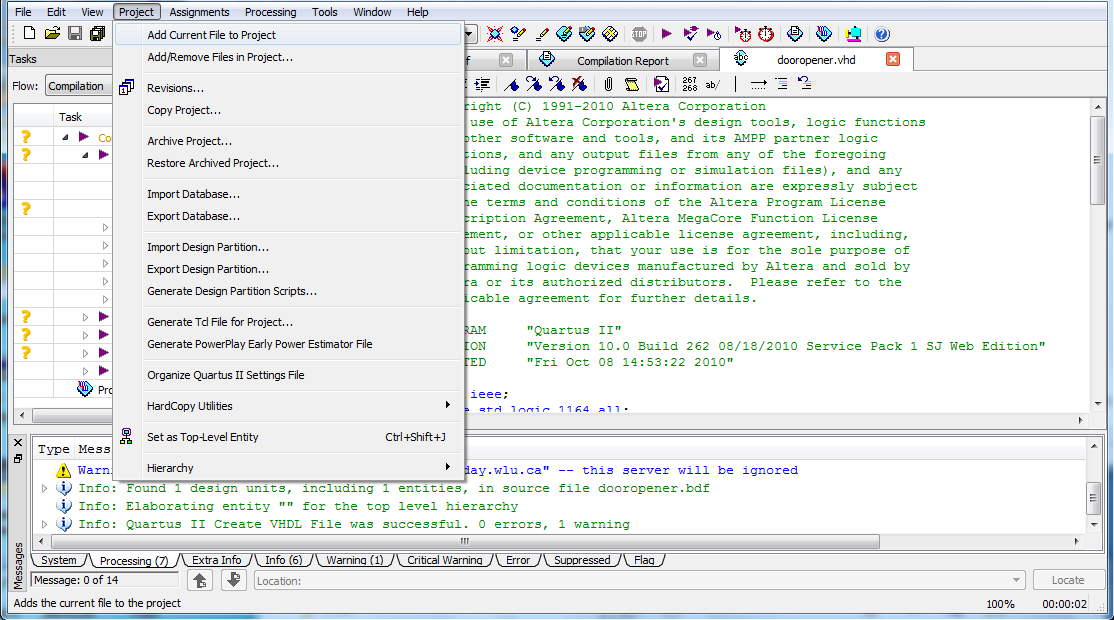

You monitor the memory resources that the embedded logic of the SignalTap II Logic Analyzer uses on your device to determine possible changes to your design. You can then route the data to device memory, or route the trigger condition to an I/O pin to use the SignalTap II Logic Analyzer in conjunction with an external logic analyzer or oscilloscope. The SignalTap II Logic Analyzer Editor provides the control to select specific nodes and choose when and how much data to capture from those nodes. After capturing the data and saving it to a SignalTap II File, you can view the data you capture in a waveform. You can make changes to the parameters and settings in that SignalTap II File with the SignalTap II Logic Analyzer Editor, which is the main window you see when you first open the SignalTap II Logic Analyzer. Each design can have only one SignalTap II File for each device you are programming. When you run a SignalTap II analysis you capture data and save it to the SignalTap II File, which is then included in your design.

stp) that contains all SignalTap II Logic Analyzer configuration data. With the SignalTap II Logic Analyzer Editor you create one SignalTap II File (.

State transition diagram altera quartus ii software#

If there were no state with the value 0, the Quartus II software would choose an arbitrary state to be the reset state.The SignalTap II Logic Analyzer Editor allows you to debug your design in real-time and at high-speed while performing an analysis in the Quartus II software. If there were no explicit reset state, the state machine would initialize to the state with value 0, which for this example is also S0. The parameters S0, S1, and S2 represent the states of the state machine.Īt power-up, the state machine initializes to the reset state S0.

The state variable reg state stores the current state of the state machine. This state machine includes a combinational always construct to model the output logic and a sequential (edge-triggered) always construct to model that state variable. Module state_machine (clk, in, reset, out) Īlways (posedge clk or posedge reset) begin The following Verilog HDL example implements a 3-state state machine. If you use constant literals to represent states, the Quartus II software uses those constant literals as the names of the states, which often makes for a less intuitive state machine. The Quartus II software uses the names of the parameters or enumeration literals when referring to the states. Note: Use parameters or enumeration literals (SystemVerilog) to represent the states of your state machine. Variables that do not meet these conditions are extracted as regular logic and not reported as a state machines. If a variable satisfies these conditions, the Quartus II software recognizes the variable as a state machine and report it in the State Machines compilation report. The variable has at most one asynchronous reset condition. The latter condition prohibits state transition logic based on arithmetic relationship among the states, for example, next_state <= state + 1. The variable is not indexed in an expression or referenced as an operand in an arithmetic expression. The variable has more than two states, in other words, it was assigned at least two distinct constant values. The values assigned to the variable are constant literals, parameters, enums (SystemVerilog), or other state variables. The variable is not declared as a module output The Quartus II software infers state machines for all registered, unsigned vector variables that satisfy the following conditions:

If you wish to disable automatic inference of state machines in Verilog HDL, set the value of the Extract State Machines logic option to Off.

State transition diagram altera quartus ii code#

By default, the Quartus II software automatically infers state machines in your Verilog HDL code by finding variables whose functionality can be replaced by a state machine without changing the simulated behavior of your design. Implementing State Machines (Verilog HDL)Ī state machine is a sequential circuit that advances through a number of states.

0 kommentar(er)

0 kommentar(er)